# Ra-01SC-P Specification

Version V1.0.1

Copyright ©2024

# **Document resume**

| Version | Date       | Develop/revise content                                                                                                                                                                                                                                                           | Edition      | Approve   |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|

| V1.0.0  | 2024.09.24 | First Edition                                                                                                                                                                                                                                                                    | Pengfei Dong | Ning Guan |

| V1.0.1  | 2025.01.02 | Add the description that the module cannot transmit without load, add the description of the input power limit of the module, add the description of the CPS and RF_EN pin control voltage, and add the description of the input power limit when the module matches the antenna | Pengfei Dong | Ning Guan |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

|         |            |                                                                                                                                                                                                                                                                                  |              |           |

## **Content**

| 1. Product overview                          | 4  |

|----------------------------------------------|----|

| 1.1. Characteristic                          | 5  |

| 2. Main parameters                           | 6  |

| 2.1. Static electricity requirement          | 6  |

| 2.2. Electrical characteristics              | 7  |

| 3. Appearance dimensions                     | 8  |

| 4. Pin definition                            | 9  |

| 5. Schematic                                 | 11 |

| 6. Design guidance                           | 12 |

| 6.1. Application Guide Circuit               | 12 |

| 6.2. Recommended PCB package size            | 14 |

| 6.3. Antenna Installation                    | 14 |

| 6.4. Power supply                            | 15 |

| 6.5. GPIO level conversion                   | 15 |

| 6.6. Software Writing                        | 17 |

| 7. FAQ                                       | 18 |

| 7.1. Factors affecting transmission distance | 18 |

| 7.2. Module usage precautions                | 18 |

| 7.3. Factors that interfere with the module  | 18 |

| 8. Storage conditions                        | 19 |

| 9. Reflow soldering curve                    | 19 |

| 10. Product packaging information            | 20 |

| 11. Contact us                               | 20 |

| Disclaimer and Copyright Notice              | 21 |

| Notice                                       | 21 |

| Important statement                          | 22 |

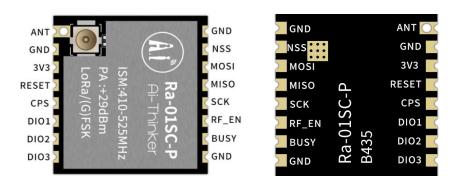

#### 1. Product overview

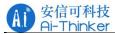

Ra-01SC-P is a LoRa series module designed and developed by Shenzhen Ai-Thinker Technology Co., Ltd. This module is used for ultra-long distance spread spectrum communication. Its RF chip LLCC68+ mainly uses LoRa<sup>™</sup> long-range modem, which is used for ultra-long distance spread spectrum communication, has strong anti-interference ability, and can minimize current consumption. With the help of SEMTECH's LoRa<sup>™</sup> patented modulation technology, the module has built-in power amplifier (PA) and low noise amplifier (LNA) on this technology, with high sensitivity exceeding -137dBm, +29dBm transmission power, long transmission distance and high reliability. At the same time, compared with traditional modulation technology, LoRa<sup>™</sup> modulation technology also has obvious advantages in anti-blocking and selection, solving the problem that traditional design solutions cannot take into account distance, anti-interference and power consumption at the same time.

It can be widely used in automatic meter reading, home building automation, security systems, remote irrigation systems, etc.

Figure 1 Main chip architecture diagram

#### 1.1. Characteristic

- Support FSK, GFSK, LoRa® modulation modes

- Support frequency band 410MHz~525MHz

- Maximum transmit power +29dBm, operating current 700mA

- High sensitivity: as low as -137dBm@SF10 125KHz

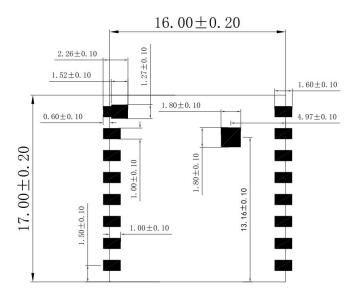

- Extremely small size  $17*16*3.2(\pm 0.2)$ MM, double-row stamp hole patch package

- Support spread factor SF5/SF6/SF7/SF8/SF9/SF10/SF11

- Low power consumption in receiving state, with a minimum receiving current of 11mA

- The module uses SPI interface, half-duplex communication, with CRC, and a data packet engine of up to 256 bytes

- Support multiple antenna installation methods, compatible with half-hole pads/through-hole pads/IPEX connector

# 2. Main parameters

Table 1 Description of the main parameters

| Model                 | Ra-01SC-P                                                     |

|-----------------------|---------------------------------------------------------------|

| Package               | SMD-16                                                        |

| Size                  | 17*16*3.2(±0.2)mm                                             |

| Antenna               | Compatible with half-hole pad/through-hole pad/IPEX connector |

| Frequency             | 410MHz~525MHz                                                 |

| Operating temperature | -40°C~ 85°C                                                   |

| Storage temperature   | -40°C~ 125°C, < 90%RH                                         |

| Power supply          | Supply voltage 3.0~3.6V, typical value 3.3V, current>1A       |

| Interface             | SPI                                                           |

| Programmable bit rate | Up to 300kbps                                                 |

## 2.1. Static electricity requirement

Ra-01SC-Pis an electrostatic sensitive device. Therefore, you need to take special precautions when carrying it.

Figure 2 ESD preventive measures

#### **Notice:**

The Ra-01SC-P module is an electrostatic sensitive device (ESD) and requires special ESD precautions that should generally be applied to ESD sensitive groups. Proper ESD handling and packaging procedures must be used throughout the handling, transportation, and operation of any application incorporating the Ra-01SC-P module. Do not touch the module with your hands or use a non-antistatic soldering iron for soldering to avoid damaging the module.

## 2.2. Electrical characteristics

**Table 2 Electrical characteristics table**

| Parameters                     | Min.      | Typical<br>value | Max.      | Unit |

|--------------------------------|-----------|------------------|-----------|------|

| Power supply voltage 3V3       | 3.0       | 3.3              | 3.6       | V    |

| IO Output High Level (VOH)     | 0.9*VDDIO | -                | VDDIO     | V    |

| IO Output Low Level (VOL)      | 0         | -                | 0.1*VDDIO | V    |

| IO Input High Level (VIH)      | 0.7*VDDIO | -                | VDDIO+0.3 | V    |

| IO Input Low Level (VIL)       | -0.3      | -                | 0.3*VDDIO | V    |

| (RF_EN/CPS)IO Input High Level | 1.2       | -                | 3.6       | V    |

| (RF_EN/CPS)IO Input Low Level  | 0         | -                | 0.3       | V    |

**Table 3 SPI interface characteristics**

| Symbol  | Description                          | Condition                                                   | Min.  | Typical value | Max. | Unit |

|---------|--------------------------------------|-------------------------------------------------------------|-------|---------------|------|------|

| Fsck    | SCK frequency                        | -                                                           | -     | -             | 10   | MHz  |

| tch     | SCK high level time                  | -                                                           | 50    | -             | -    | ns   |

| tel     | SCK low level time                   | -                                                           | 50    | -             | -    | ns   |

| trise   | SCK rise time                        | -                                                           | -     | 5             | -    | ns   |

| tfall   | SCK fall time                        | -                                                           | -     | 5             | -    | ns   |

| tsetup  | MOSI setup time                      | setup time From MOSI change to SCK rising edge -            |       | -             | -    | ns   |

| thold   | MOSI hold time                       | From SCK rising edge to MOSI change                         | 20    | -             | -    | ns   |

| tnsetup | NSS setup time                       | me From NSS falling edge to SCK rising edge                 |       | -             | -    | ns   |

| tnhold  | NSS hold time                        | From SCK falling edge to<br>NSS rising edge, normal<br>mode | 100 - |               | -    | ns   |

| tnhigh  | NSS high time of SPI access interval |                                                             | -     | -             | ns   |      |

| T_DATA  | DATA hold and setup time             | -                                                           | 250   | -             | -    | ns   |

| Fsck    | SCK frequency                        |                                                             |       | -             | -    | ns   |

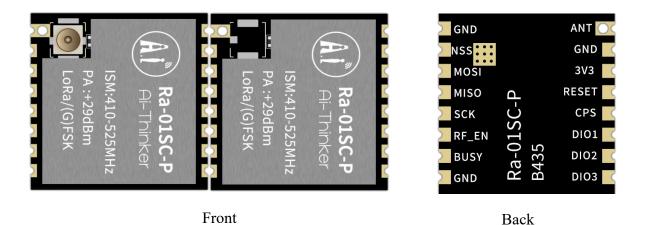

# 3. Appearance dimensions

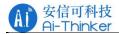

Figure 3 Appearance(rendering is for reference only, the actual object shall prevail)

Figure 4 Dimensions (unit: mm)

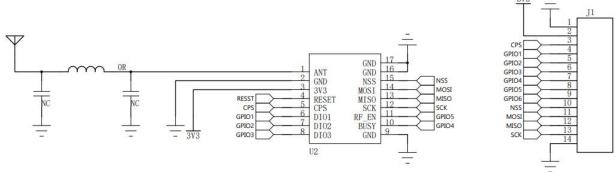

## 4. Pin definition

Ra-01SC-P module has a total of 16 pins, as shown in the pin diagram. The pin function definition table is the interface definition.

Front Back Figure 5 Pin diagram

**Table 4 Pin function definition table**

| No.  | Name  | Function                                                                                                                                                                 |  |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | ANT   | Connect antenna                                                                                                                                                          |  |

| 2    | GND   | Ground                                                                                                                                                                   |  |

| 3    | 3V3   | Typical value 3.3V power supply                                                                                                                                          |  |

| 4    | RESET | Reset pin                                                                                                                                                                |  |

| 5    | CPS   | FEM chip TX pass-through enable pin, in transmit mode, this pin is low level R F and is directly output without PA amplification, and is internally pulled up by default |  |

| 6    | DIO1  | Digital IO1 software configuration                                                                                                                                       |  |

| 7    | DIO2  | Digital IO2 software configuration                                                                                                                                       |  |

| 8    | DIO3  | Digital IO3 software configuration                                                                                                                                       |  |

| 9    | GND   | Ground                                                                                                                                                                   |  |

| 10   | BUSY  | Status indication pin                                                                                                                                                    |  |

| 11   | RF_EN | FEM chip enable pin, high level is effective, the module is pulled up by default;<br>High level is in working state, low level is in sleep state                         |  |

| 12   | SCK   | SPI clock input                                                                                                                                                          |  |

| 13   | MISO  | SPI data output                                                                                                                                                          |  |

| 14   | MOSI  | SPI data input                                                                                                                                                           |  |

| 15   | NSS   | SPI chip select input                                                                                                                                                    |  |

| 16   | GND   | Ground                                                                                                                                                                   |  |

| EPAD | GND   | Ground, reliable grounding is required to facilitate heat dissipation                                                                                                    |  |

The general IO pins of LLCC68+ are available in LoRa™ mode. Their mapping relationship depends on the configuration of the two registers RegDioMapping1 and RegDioMapping2.

Table 5 IO port function mapping table

| Operation Mode | DIOx<br>Mapping | DIO3                | DIO2                      | DIO1                      |

|----------------|-----------------|---------------------|---------------------------|---------------------------|

|                | 00              | CadDone             | Fhss<br>Change<br>Channel | RxRimeout                 |

| All            | 01              | Valid<br>Header     | Fhss<br>Change<br>Channel | Fhss<br>Change<br>Channel |

|                | 10              | PayloadCrc<br>Error | Fhss<br>Change<br>Channel | CadDetected               |

|                | 11              | -                   | -                         | -                         |

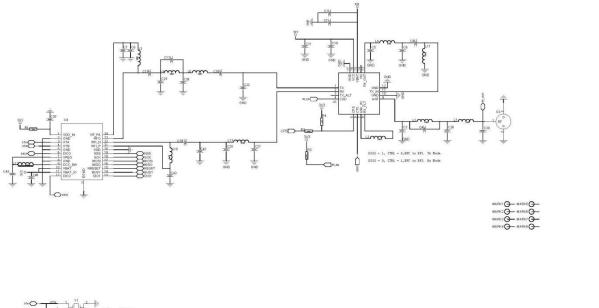

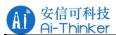

# 5. Schematic

Figure 6 Schematic diagram

# 6. Design guidance

#### 6.1. Application Guide Circuit

#### (1) Special pin description

#### About CPS pin

CPS is the TX pass-through control pin of the built-in PA chip of the module, with an internal pull-up resistor of 10K (that is, R F is in PA amplification output mode in the default transmission mode). When the module is in transmission mode:

- ✓ This pin is high level, and the module's R F is amplified and output by PA;

- ✓ When this pin is low level, the module's R F is directly output without being amplified by PA;

- ✓ The logic of this pin is invalid in the receiving state and needs to be set to a low level when low power consumption;

#### ■ About RF EN pin

RF\_EN is the enable pin of the module's built-in PA chip. When the pin is high, the module's RF is in normal transceiver state; when the pin is low, the module's RF function is turned off, which can reduce the module's power consumption.

ModeRF\_ENFEM power off0FEM working1

Table 6 RF switch truth table

The module defaults to BOM, CPS and RF\_EN have internal pull-up resistors of 10K (i.e., they are in normal amplification and transceiver state by default). If a low-power working scenario is required, please use an external MCU to control this pin to a low level state. When the level is low, the default pull-up resistor of this pin may have leakage current. If the built-in pull-up resistor is not required, please contact Anxin to modify the BOM.

In summary, the module has two BOM configurations.

Configuration 1. CPS and RF\_EN have built-in pull-up resistors of 10K (default BOM configuration)

Configuration 2. CPS and RF\_EN have built-in pull-up resistors without mounting, and require IO port control of the peripheral MCU

#### (2) Typical application circuit

Figure 7 Typical application circuit

- It is recommended that CPS and RF\_EN be used for the I/O control modules of an external MCU to achieve low power consumption.

- The transmit power level configured for module LCC68 cannot be greater than 3dBm. Otherwise, too large a power level will burn out the PA.

- Do not leave the antenna port of the module in the suspended state when the module is in TX transmission, because the VSWR is large during no-load transmission, and the FEM chip has a higher risk of damage; If the ANT port cannot be avoided, the maximum TX input signal power should not exceed 0dBm to ensure that the chip is not damaged.

- The CPS and RF\_EN pin voltage of the module must be the recommended value (1.2-3.6V), and the pin voltage cannot exceed the power supply voltage of module 3V3. Ensure that module 3V3 is powered on before CPS and RF EN.

- During the antenna matching and debugging process, the impedance may not match, resulting in a large VSWR. During this process, it is recommended not to directly generate saturated power to avoid excessive damage to the chip due to VSWR. After the antenna impedance debugging is completed, the saturation power is generated again.

- The power supply current must meet the specifications. If the current is limited, the saturated power cannot be pushed up.

#### (3) Other instruction

■ The communication interface with the master MCU, in addition to the SPI interface, also needs to connect BUSY/DIO1 to the IO port of the master MCU.

Figure 8 BUSY/DIO1 application considerations

■ The antenna is soldered on the main control board. It is recommended to reserve a pie-shaped matching circuit at the antenna interface.

#### 6.2. Recommended PCB package size

Figure 9 Recommended PCB package dimensions (unit: mm)

#### 6.3. Antenna Installation

- Ra-01SC-P requires an external antenna. There is a half-hole pad on the module that can be connected to the mainboard.

- In order for the antenna to achieve the best effect, the antenna should be installed away from metal parts.

- The antenna installation structure has a great impact on the performance of the module.

Make sure that the antenna is exposed, preferably vertically upward. When the module is installed inside the casing, use a high-quality antenna extension cable to extend the antenna to the outside of the casing.

■ The antenna must not be installed inside the metal casing, which will greatly reduce the transmission distance.

#### 6.4. Power supply

- Recommend 3.3V voltage, peak current above 1A.

- If using DC-DC, it is recommended to control the ripple within 100mV.

- It is recommended to reserve a position for dynamic response capacitors in the DC-DC power supply circuit, which can optimize the output ripple when the load changes greatly.

- It is recommended to add ESD devices to the 3.3V power supply interface.

- When designing the power supply circuit for the module, it is recommended to retain more than 30% of the power supply current margin, which is conducive to long-term stable operation of the whole machine.

- Please pay attention to the correct connection of the positive and negative poles of the power supply. Reverse connection may cause permanent damage to the module.

Figure 10 DC-DC buck circuit

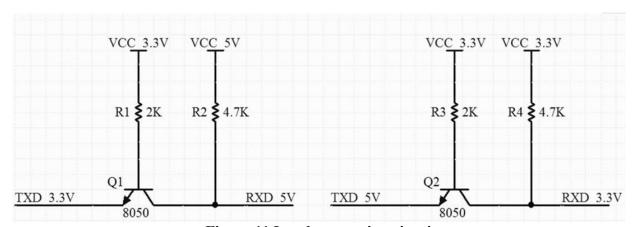

#### 6.5. GPIO level conversion

- Some IO ports are connected to the module. If you need to use them, it is recommended to connect a 10-100 ohm resistor in series to the IO ports. This can suppress overshoot and make the levels on both sides more stable. It is helpful for EMI and ESD.

- For the pull-up and pull-down of special IO ports, please refer to the instructions in the specification, which will affect the startup configuration of the module.

- The IO port of the module is 3.3V. If the IO port levels of the main control and the module do not match, a level conversion circuit needs to be added.

■ If the IO port is directly connected to a peripheral interface, or terminals such as a pin header, it is recommended to reserve ESD devices near the terminals in the IO port routing.

Figure 11 Level conversion circuit

#### 6.6. Software Writing

- The maximum input power of the FEM chip cannot exceed +3dBm, otherwise the FEM chip will be burned. Users need to strictly configure the output power of LLCC68, 0dBm to 3dBm is recommended.

- This module is LLCC68+peripheral circuit, users can operate it completely according to the LLCC68 chip manual.

- DIO1/DIO2 is a general IO port that can be configured for multiple functions.

- The control of the RF switch TX/RX can be controlled by an external MCU; it can also be jointly controlled by an external MCU and DIO2 of LLCC68.

- Differences between LLCC68 and SX1262/SX1268:

- (1) SX1262/SX1268 supports spreading factors SF5, SF6, SF7, SF8, SF9, SF10, SF11, SF12;

SX1262/SX1268 can set spreading factors and receiving bandwidth

LoRa@ Rx/Tx, BW = 7.8 - 500 kHz,

SF5 TO SF12, BR=0.018 - 62.5 Kb/S

(2) LLCC68 supports spreading factors SF5, SF6, SF7, SF8, SF9, SF10, and SF11;

LLCC68 can set spreading factors and receiving bandwidth

LoRa@Rx/Tx, BW = 125 - 250 - 500 kHz,

LoRa@, SF=5-6-7-8-9 for BW=125kHz,

LoRa@, SF=5-6-7-8-9-10 for BW =250 kHz,

LoRa@, SF=5-6-7-8-9-10-11 for BW=500 kHz.

## **7. FAQ**

## 7.1. Factors affecting transmission distance

- When there is a straight-line communication obstacle, the communication distance will be attenuated accordingly.

- Temperature, humidity, and co-frequency interference will lead to an increase in the communication packet loss rate.

- The ground absorbs and reflects radio waves, so the test effect is poor near the ground.

- Seawater has a strong ability to absorb radio waves, so the test effect is poor at the seaside.

- If there are metal objects near the antenna, or it is placed in a metal shell, the signal attenuation will be very serious.

- The power register is set incorrectly, and the air rate is set too high (the higher the air rate, the closer the distance).

- The power supply low voltage at room temperature is lower than the recommended value. The lower the voltage, the lower the power.

- The antenna used is poorly matched with the module or the antenna itself has quality problems.

### 7.2. Module usage precautions

- Check the power supply to ensure that it is within the recommended power supply voltage. If it exceeds the maximum value, the module will be permanently damaged.

- Check the stability of the power supply. The voltage cannot fluctuate frequently and significantly.

- Ensure anti-static operation during installation and use, and high-frequency components are electrostatically sensitive.

- Ensure that the humidity during installation and use is not too high. Some components are humidity-sensitive devices.

- If there is no special requirement, it is not recommended to use it at too high or too low temperature.

#### 7.3. Factors that interfere with the module

- There is interference from the same frequency signal nearby, stay away from the interference source or change the frequency or channel to avoid interference.

- The clock waveform on the SPI is not standard, check whether there is interference on the SPI line, and the SPI bus line should not be too long.

- Unsatisfactory power supply may also cause garbled code, so the reliability of the power supply must be ensured.

- Poor or too long extension line or feeder line will also cause a high bit error rate.

# 8. Storage conditions

Products sealed in moisture-proof bags should be stored in a non-condensing atmosphere of  $<40^{\circ}\text{C}/90\%\text{RH}$ .

The module's moisture sensitivity level MSL is level 3.

After the vacuum bag is unsealed, it must be used within 168 hours at  $25 \pm 5$  °C/60%RH, otherwise it needs to be baked before it can be put online again.

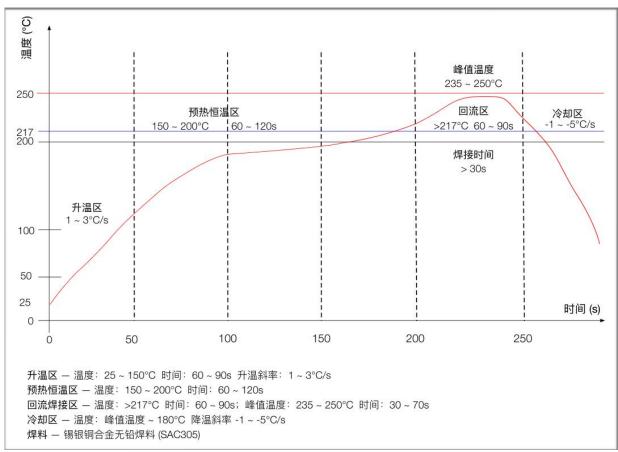

# 9. Reflow soldering curve

Figure 12 Reflow soldering curve

# 10. Product packaging information

As shown in the figure below, the packaging of Ra-01SC-P is braided tape, 800pcs/reel. As shown in the figure below:

13 Packaging and taping diagram

## 11.Contact us

<u>Ai-Thinker official website</u> <u>Office forum</u> <u>Develop DOCS</u>

<u>LinkedIn</u> <u>Tmall shop</u> <u>Taobao shop</u> <u>Alibaba shop</u>

Technical support email: support@aithinker.com

Domestic business cooperation: sales@aithinker.com

Overseas business cooperation: overseas@aithinker.com

Company Address: Room 403-405,408-410, Block C, Huafeng Smart Innovation Port, Gushu

2nd Road, Xixiang, Baoan District, Shenzhen.

Tel: +86-0755-29162996

WeChat mini program

WeChat official account

# **Disclaimer and Copyright Notice**

The information in this document, including the URL address for reference, is subject to change without notice.

The document is provided "as is" without any warranty, including any warranty of merchantability, fitness for a particular purpose or non-infringement, and any warranty mentioned elsewhere in any proposal, specification or sample. This document does not assume any liability, including liability for infringement of any patent rights arising from the use of the information in this document. This document does not grant any intellectual property rights license, whether express or implied, by estoppel or otherwise.

The test data obtained in this article are all obtained by Ai-Thinker Laboratory, and the actual results may vary slightly.

All trade names, trademarks and registered trademarks mentioned in this article are the property of their respective owners and are hereby declared.

The final right of interpretation belongs to Shenzhen Ai-Thinker Technology Co., Ltd.

#### **Notice**

The contents of this manual may be changed due to product version upgrades or other reasons.

Shenzhen Ai-Thinker Technology Co., Ltd. reserves the right to modify the contents of this manual without any notice or reminder.

This manual is only used as a guide. Shenzhen Ai-Thinker Technology Co., Ltd. tries its best to provide accurate information in this manual, but Shenzhen Ai-Thinker Technology Co., Ltd. does not ensure that the contents of the manual are completely error-free, and all statements, information and suggestions in this manual do not constitute any express or implied warranty.

## Important statement

Ai-Thinker may provide technical and reliability data "as is" (including data sheets), design resources (including design for reference purposes), application or other design recommendations, network tools, security information and other resources (the "these resources") and without warranty without express or implied warranty, including without limitation, adaptability for a particular purpose or infringement of intellectual property rights of any third party. And specifically declares that it is not liable for any inevitable or incidental losses arising from the application or the use of any company products and circuits.

Ai-Thinker reserves the right to the information released in this document (including but not limited to the indicators and product description) and any changes to the Company without notice to automatically replace and replace all the information provided in the previous version of the same document number document.

These resources are available to skilled developers who design Essence products. You will assume all responsibilities for the following: (1) select the appropriate optional products for your application; (2) design, verify, and run your application and products during the full life cycle; and (3) ensure that your application meets all corresponding standards, norms and laws, and any other functional.

Ai-Thinker authorizes you to use these resources only for the application of the Ai-Thinker products described in this resource. Without the permission of Ai-Thinker, no unit or individual shall copy or copy part or all of these resources without authorization, and shall not spread them in any form. You are not entitled to use any other Principal or any third party intellectual property. You shall fully indemnify you for any claims, damages, costs, losses and debts incurred by the result of the use of these resources.

The products available by Ai-Thinker are subject to the terms of sales or other applicable terms attached to the products. Ai-Thinker may provide these resources does not extend or otherwise change the applicable warranty or warranty disclaimer for the product release.